# DG200, DG201

December 1993

#### **CMOS Dual/Quad SPST Analog Switches**

#### **Features**

- Switches Greater than 28V<sub>P-P</sub> Signals with ±15 Supplies

- Break-Before-Make Switching  $t_{\mbox{OFF}}$  250ns,  $t_{\mbox{ON}}$  700ns Typical

- TTL, DTL, CMOS, PMOS Compatible

- · Non-Latching with Supply Turn-Off

- · Complete Monolithic Construction

- · Industry Standard (DG200, DG201)

#### **Applications**

- · Data Acquisition

- · Sample and Hold Circuits

- Operational Amplifier Gain Switching Networks

#### Description

The DG200 and DG201 solid state analog gates are designed using an improved, high voltage CMOS monolithic technology. They provide ease-of-use and performance advantages not previously available from solid state switches. Destructive latch-up of solid state analog gates has been eliminated by Harris's CMOS technology.

The DG200 and DG201 are completely specification and pinout compatible with the industry standard devices.

#### **Ordering Information**

| PART NUMBER  | TEMPERATURE     | PACKAGE             |

|--------------|-----------------|---------------------|

| DG200AA      | -55°C to +125°C | 10 Pin Metal Can    |

| DG200AK      | -55°C to +125°C | 14 Lead Ceramic DIP |

| DG200BA      | -25°C to +85°C  | 10 Pin Metal Can    |

| DG200BK      | -25°C to +85°C  | 14 Lead Ceramic DIP |

| DG200CJ      | 0°C to +70°C    | 14 Lead Plastic DIP |

| DG200AA/883B | -55°C to +125°C | 10 Pin Metal Can    |

| DG200AK/883B | -55°C to +125°C | 14 Lead Ceramic DIP |

| DG201AK      | -55°C to +125°C | 16 Lead Ceramic DIP |

| DG201BK      | -25°C to +85°C  | 16 Lead Ceramic DIP |

| DG201CJ      | 0°C to +70°C    | 16 Lead Plastic DIP |

| DG201AK/883B | -55°C to +125°C | 16 Lead Ceramic DIP |

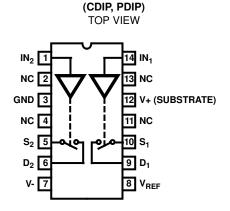

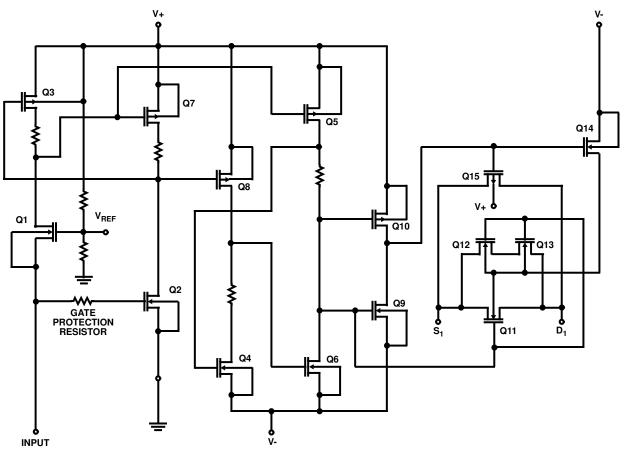

#### **Pinouts**

**DG200**

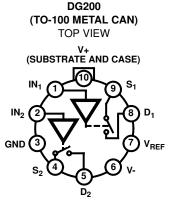

DG201

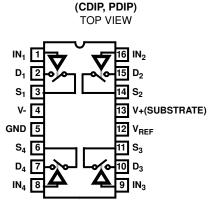

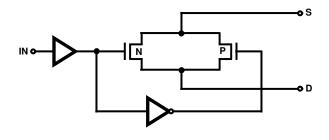

# Schematic Diagram (1/2 DG200, 1/4 DG201)

### Functional Diagram

DG200, DG201 SWITCH CELL

#### Specifications DG200

# Absolute Maximum Ratings Thermal Information V+, V <36V</th> Thermal Resistance θ JA θ JC V+ - V<sub>D</sub> <30V</td> Ceramic DIP Package 95°C/W 24°C/W V<sub>D</sub> - V <30V</td> Plastic DIP Package 100°C/W V<sub>D</sub> - V<sub>S</sub> <28V</td> Metal Can Package 136°C/W 65°C/W V<sub>IN</sub> - GND <20V</td> Operating Temperature Range Storage Temperature Range -65°C to +150°C "A" Suffix .-55°C to +125°C Lead Temperature (Soldering 10s) +300°C "B" Suffix .-25°C to +85°C "C" Suffix 0°C to +70°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Electrical Specifications** $(T_A = +25^{\circ}C, V_{+} = +15V, V_{-} = -15V)$

|                                                                       |                                                                                                                    | MILITARY |          |        | COMMERCIAL / INDUSTRIAL |          |                   |       |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------|----------|--------|-------------------------|----------|-------------------|-------|

| PARAMETER                                                             | TEST CONDITIONS                                                                                                    | -55°C    | +25°C    | +125°C | 0°C TO<br>-25°C         | +25°C    | +70°C TO<br>+85°C | UNITS |

| Input Logic Current, $V_{IN} = 0.8V$ (Notes 2, 3) $I_{IN(ON)}$        |                                                                                                                    | ±10      | ±1       | ±10    | -                       | ±10      | ±10               | μΑ    |

| Input Logic Current,<br>I <sub>N(OFF)</sub>                           |                                                                                                                    |          | ±1       | ±10    | -                       | ±10      | ±10               | μΑ    |

| Drain-Source On Resistance, r <sub>DS(ON)</sub>                       | $I_S = 10$ mA, $V_{ANALOG} = \pm 10$ V                                                                             | 70       | 70       | 100    | 80                      | 80       | 100               | Ω     |

| Channel-to-Channel r <sub>DS(ON)</sub> Match, r <sub>DS(ON)</sub>     |                                                                                                                    | -        | 25 (Typ) | -      | -                       | 30 (Typ) | -                 | Ω     |

| Minimum Analog Signal<br>Handling Capability,<br>V <sub>ANALOG</sub>  |                                                                                                                    | -        | ±15V     | -      | -                       | ±15V     | -                 | V     |

| Switch OFF Leakage<br>Current, I <sub>D(OFF)</sub>                    | $V_{ANALOG} = -14V \text{ to } +14V$                                                                               | -        | ±2       | 100    | -                       | ±5       | 100               | nA    |

| Switch OFF Leakage<br>Current, I <sub>S(OFF)</sub>                    | $V_{ANALOG} = -14V \text{ to } +14V$                                                                               | -        | ±2       | 100    | -                       | ±5       | 100               | nA    |

| Switch ON Leakage Current, I <sub>D(ON)</sub> + I <sub>S(ON)</sub>    | $V_D = V_S = -14V \text{ to } +14V$                                                                                | -        | ±2       | 200    | -                       | ±10      | 200               | nA    |

| Switch "ON" Time (Note 1), t <sub>ON</sub>                            | $R_L = 1k\Omega$ , $V_{ANALOG} =$<br>-10V to +10V (Figure 5)                                                       | -        | 1.0      | -      | -                       | 1.0      | -                 | μs    |

| Switch "OFF" Time, t <sub>OFF</sub>                                   | $R_L = 1k\Omega$ , $V_{ANALOG} =$<br>-10V to +10V (Figure 5)                                                       | -        | 0.5      | -      | -                       | 0.5      | -                 | μs    |

| Charge Injection, Q <sub>(INJ.)</sub>                                 | Figure 6                                                                                                           | -        | 15 (Typ) | -      | -                       | 20 (Typ) | -                 | mV    |

| Minimum Off Isolation<br>Rejection Ratio, OIRR                        | $\begin{split} &f=1\text{MHz}, \ R_L=100\Omega, \\ &C_L \leq 5\text{pF} \\ &(\text{Figure 7, Note 1}) \end{split}$ | -        | 54 (Typ) | -      | -                       | 50 (Typ) | -                 | dB    |

| +Power Supply<br>Quiescent Current, I <sub>V1</sub>                   | $V_{IN} = 0V$ or $V_{IN} = 5V$                                                                                     | 1000     | 1000     | 2000   | 1000                    | 1000     | 2000              | μΑ    |

| -Power Supply<br>Quiescent Current, I <sub>V2</sub>                   |                                                                                                                    | 1000     | 1000     | 2000   | 1000                    | 1000     | 2000              | μА    |

| Minimum Channel to<br>Channel Cross Coupling<br>Rejection Ratio, CCRR | One Channel Off                                                                                                    | -        | 54 (Typ) | -      | -                       | 50 (Typ) | -                 | dB    |

#### NOTES:

- 1. Pull Down Resistor must be  $\leq 2k\Omega$ .

- 2. Typical values are for design aid only, not guaranteed and not subject to production testing.

- 3. All channels are turned off by high "1" logic inputs and all channels are turned on by low "0" inputs; however 0.8V to 2.4V describes the minimum range for switching properly. Peak input current required for transition is typically -120µA.

#### Specifications DG201

#### **Absolute Maximum Ratings Thermal Information** V+ to V-.....<36V Thermal Resistance 24°C/W V+ to V<sub>D</sub>.....<30V Ceramic DIP Package . . . . . . . . . . . . 80°C/W $V_D$ to $V_S$ .....<28V Operating Temperature Range V<sub>REF</sub> to V-.....<33V Storage Temperature Range . . . . . . . . -65°C to +150°C Lead Temperature (Soldering 10s).....+300°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Electrical Specifications** $(T_A = +25^{\circ}C, V_{+} = +15V, V_{-} = -15V)$

|                                                                       |                                                              | MILITARY |           | СОММЕ  |                 |           |                   |       |

|-----------------------------------------------------------------------|--------------------------------------------------------------|----------|-----------|--------|-----------------|-----------|-------------------|-------|

| PARAMETER                                                             | TEST CONDITIONS                                              | -55°C    | +25°C     | +125°C | 0°C TO<br>-25°C | +25°C     | +70°C TO<br>+85°C | UNITS |

| Input Logic Current,<br>I <sub>IN(ON)</sub>                           | V <sub>IN</sub> = 0.8V (Note 1)                              | 10       | ±1        | 10     | ±1              | ±1        | 10                | μΑ    |

| Input Logic Current,<br>I <sub>N(OFF)</sub>                           | V <sub>IN</sub> = 2.4V (Note 1)                              | 10       | ±1        | 10     | ±1              | ±1        | 10                | μΑ    |

| Drain-Source On Resistance, r <sub>DS(ON)</sub>                       | I <sub>S</sub> = 10mA, V <sub>ANALOG</sub> = ±10V            | 80       | 80        | 125    | 100             | 100       | 125               | Ω     |

| Channel-to-Channel r <sub>DS(ON)</sub> Match, r <sub>DS(ON)</sub>     |                                                              | -        | 25 (Typ)  | -      | -               | 30 (Typ)  | -                 | Ω     |

| Minimum Analog Signal<br>Handling Capability,<br>V <sub>ANALOG</sub>  |                                                              | -        | ±15 (Typ) | -      | -               | ±15 (Typ) | -                 | V     |

| Switch OFF Leakage<br>Current, I <sub>D(OFF)</sub>                    | $V_{ANALOG} = -14V \text{ to } +14V$                         | -        | ±1        | 100    | -               | ±5        | 100               | nA    |

| Switch OFF Leakage<br>Current, I <sub>S(OFF)</sub>                    | $V_{ANALOG} = -14V \text{ to } +14V$                         | -        | ±1        | 100    | -               | ±5        | 100               | nA    |

| Switch ON Leakage Current, I <sub>D(ON)</sub> + I <sub>S(ON)</sub>    | $V_D = V_S = -14V \text{ to } +14V$                          | -        | ±2        | 200    | -               | ±5        | 200               | nA    |

| Switch "ON" Time<br>(Note 2), t <sub>ON</sub>                         | $R_L = 1k\Omega$ , $V_{ANALOG} =$ -10V to +10V (Figure 5)    | -        | 1.0       | -      | -               | 1.0       | -                 | μs    |

| Switch "OFF" Time<br>(Note 2), t <sub>OFF</sub>                       | $R_L = 1k\Omega$ , $V_{ANALOG} =$<br>-10V to +10V (Figure 5) | -        | 0.5       | -      | -               | 0.5       | -                 | μs    |

| Charge Injection, Q <sub>(INJ.)</sub>                                 | Figure 6                                                     | -        | 15 (Typ)  | -      | -               | 20 (Typ)  | -                 | mV    |

| Minimum Off Isolation<br>Rejection Ratio, OIRR                        | $f = 1 MHz, R_L = 100\Omega,$ $C_L \le 5 pF, (Figure 7)$     | -        | 54 (Typ)  | -      | -               | 50 (Typ)  | -                 | dB    |

| +Power Supply<br>Quiescent Current, I+Q                               | $V_{IN} = 0V$ or $V_{IN} = 5V$                               | 2000     | 1000      | 2000   | 2000            | 1000      | 2000              | μΑ    |

| -Power Supply<br>Quiescent Current, I-Q                               |                                                              | 2000     | 1000      | 2000   | 2000            | 1000      | 2000              | μΑ    |

| Minimum Channel to<br>Channel Cross Coupling<br>Rejection Ratio, CCRR | One Channel Off                                              | 1        | 54 (Typ)  | -      | -               | 50 (Typ)  | -                 | dB    |

#### NOTES:

- 1. Typical values are for design aid only, not guaranteed and not subject to production testing.

- 2. All channels are turned off by high "1" logic inputs and all channels are turned on by low "0" inputs; however 0.8V to 2.4V describes the minimum range for switching properly. Peak input current required for transition is typically -120µA.

#### **Performance Curves**

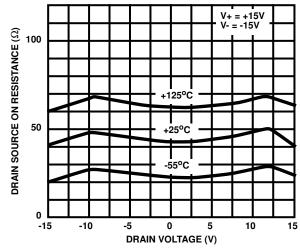

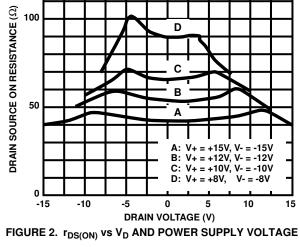

FIGURE 1.  $R_{DS(ON)}$  vs  $V_D$  and temperature

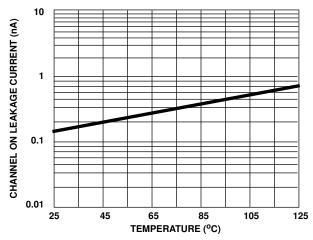

FIGURE 3.  $I_{D(ON)}$  vs TEMPERATURE

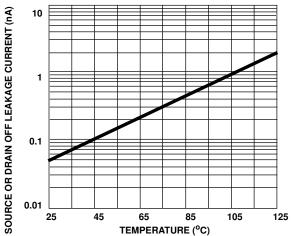

FIGURE 4.  $I_{S(OFF)}$  OR  $I_{D(OFF)}$  vs TEMPERATURE

#### Pin Description

|     | DG200 (14 LEAD DIP) |                                            |  |  |  |  |

|-----|---------------------|--------------------------------------------|--|--|--|--|

| PIN | SYMBOL              | DESCRIPTION                                |  |  |  |  |

| 1   | IN <sub>2</sub>     | Logic control for switch 2                 |  |  |  |  |

| 2   | NC                  | No Connection                              |  |  |  |  |

| 3   | GND                 | Ground Terminal (Logic Common)             |  |  |  |  |

| 4   | NC                  | No Connection                              |  |  |  |  |

| 5   | S <sub>2</sub>      | Source (input) terminal for switch 2       |  |  |  |  |

| 6   | D <sub>2</sub>      | Drain (output) terminal for switch 2       |  |  |  |  |

| 7   | V-                  | Negative power supply terminal             |  |  |  |  |

| 8   | $V_{REF}$           | Logic reference voltage                    |  |  |  |  |

| 9   | D <sub>1</sub>      | Drain (output) terminal for switch 1       |  |  |  |  |

| 10  | S <sub>1</sub>      | Source (input) terminal for switch 1       |  |  |  |  |

| 11  | NC                  | No Connection                              |  |  |  |  |

| 12  | V+                  | Positive power supply terminal (substrate) |  |  |  |  |

| 13  | NC                  | No Connection                              |  |  |  |  |

| 14  | IN <sub>1</sub>     | Source (input) terminal for switch 1       |  |  |  |  |

| DG201 (16 LEAD DIP) |                 |                                            |  |  |  |

|---------------------|-----------------|--------------------------------------------|--|--|--|

| PIN                 | SYMBOL          | DESCRIPTION                                |  |  |  |

| 1                   | IN <sub>1</sub> | Logic control for switch 1                 |  |  |  |

| 2                   | D <sub>1</sub>  | Drain (output) terminal for switch 1       |  |  |  |

| 3                   | S <sub>1</sub>  | Source (input) terminal for switch 1       |  |  |  |

| 4                   | V-              | Negative power supply terminal             |  |  |  |

| 5                   | GND             | Ground terminal (Logic Common)             |  |  |  |

| 6                   | S <sub>4</sub>  | Source (input) terminal for switch 4       |  |  |  |

| 7                   | D <sub>4</sub>  | Drain (output) terminal for switch 4       |  |  |  |

| 8                   | IN <sub>4</sub> | Logic control for switch 4                 |  |  |  |

| 9                   | IN <sub>3</sub> | Logic control for switch 3                 |  |  |  |

| 10                  | $D_3$           | Drain (output) terminal for switch 3       |  |  |  |

| 11                  | S <sub>3</sub>  | Source (input) terminal for switch 3       |  |  |  |

| 12                  | $V_{REF}$       | Logic reference voltage                    |  |  |  |

| 13                  | V+              | Positive power supply terminal (substrate) |  |  |  |

| 14                  | S <sub>2</sub>  | Source (input) terminal for switch 2       |  |  |  |

| 15                  | $D_2$           | Drain (output) terminal for switch 2       |  |  |  |

| 16                  | IN <sub>2</sub> | Logic control for switch 2                 |  |  |  |

#### **Test Circuits ANALOG INPUT 10V** ANALOG INPUT 10V $V_{OUT}$ LOGIC INPUT ≤**2k**Ω 10pF 1kΩ $V_{OUT}$ LOGIC INPUT NOTE: All channels are turned off by high "1" logic inputs and all channels are turned on by low "0" inputs; however 0.8V to 10,000pF 2.4V describes the minimum range for switching properly. Peak input current required for transition is typically -120µA. FIGURE 6. FIGURE 5. 2V<sub>P-P</sub> AT 1MHz **LOGIC** 51 $\Omega$ INPUT $V_{OUT}$

100Ω

FIGURE 7.

Pull Down Resistor must be  $\leq$  2k $\Omega$ .

#### **Typical Applications**

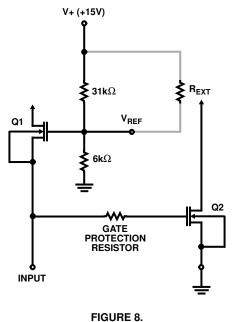

#### Using the V<sub>REF</sub> Terminal

The DG200 and DG201 have an internal voltage divider setting the TTL threshold on the input control lines for V+ equal to +15V. The schematic shown in Figure 8 with nominal resistor values, gives approximately 2.4V on the  $V_{\mbox{\scriptsize REF}}$  pin. As the TTL input signal goes from +0.8V to +2.4V, Q1 and Q2 switch states to turn the switch ON and OFF.

If the power supply voltage is less than +15V, then a resistor must be added between V+ and the  $V_{REF}$  pin, to restore +2.4V at  $V_{REF}$ . The table shows the value of this resistor for various supply voltages, to maintain TTL compatibility. If CMOS logic levels on a +5V supply are being used, the threshold shifts are less critical, but a separate column of suitable values is given in the table. For logic swings of -5V to +5V, no resistor is needed.

In general, the "low" logic level should be <0.8V to prevent Q1 and Q2 from both being ON together (this will cause incorrect switch function).

TABLE 1.

| V+ SUPPLY (V) | TTL RESISTOR ( $k\Omega$ ) | CMOS RESISTOR ( $k\Omega$ ) |

|---------------|----------------------------|-----------------------------|

| +15           | -                          | -                           |

| +12           | 100                        | -                           |

| +10           | 51                         | -                           |

| +9            | (34)                       | 34                          |

| +8            | (27)                       | 27                          |

| +7            | 18                         | 18                          |

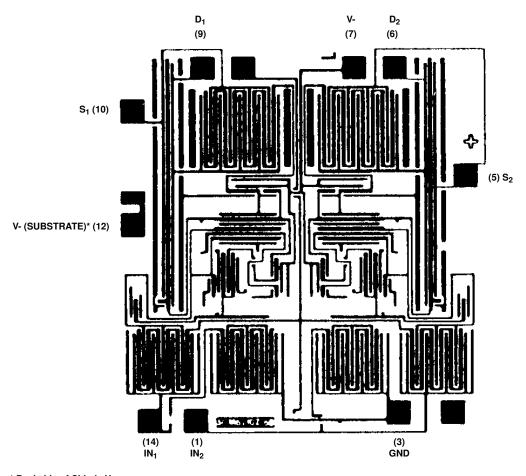

#### **Metallization Topology**

#### **DIE DIMENSIONS:**

74 x 77 x 14  $\pm$  1mils

#### **METALLIZATION:**

Type: Al

Thickness: 10kÅ ± 1kÅ

#### **GLASSIVATION:**

Type:  $SiO_2/Si_3N_4$   $SiO_2$  Thickness:  $7k\mathring{A} \pm 1.4k\mathring{A}$   $Si_3N_4$  Thickness:  $8k\mathring{A} \pm 1.2k\mathring{A}$

## WORST CASE CURRENT DENSITY: $1 \times 10^5 \text{ A/cm}^2$

#### Metallization Mask Layout

DG200

<sup>\*</sup> Backside of Chip is V+

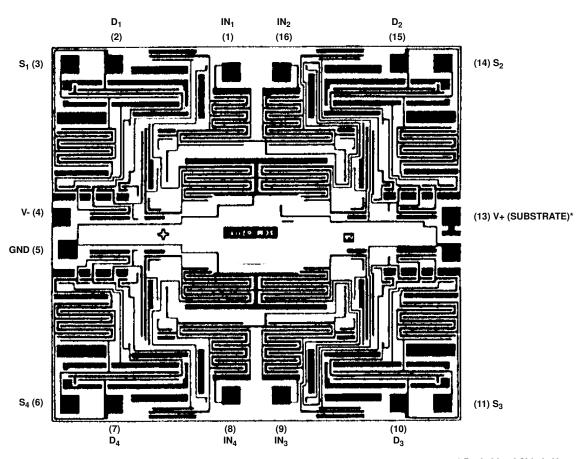

#### **Metallization Topology**

#### **DIE DIMENSIONS:**

94 x 101 x 14  $\pm$  1mils

#### **METALLIZATION:**

Type: Al

Thickness: 10kÅ ± 1kÅ

#### **GLASSIVATION:**

Type:  $SiO_2/Si_3N_4$  $SiO_2$  Thickness:  $7k\mathring{A} \pm 1.4k\mathring{A}$  $Si_3N_4$  Thickness:  $8k\mathring{A} \pm 1.2k\mathring{A}$

## WORST CASE CURRENT DENSITY: $1 \times 10^5 \text{ A/cm}^2$

#### Metallization Mask Layout

#### DG201

\* Backside of Chip is V+