# **CA3046**

# General Purpose NPN Transistor Arrays

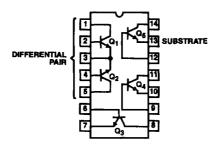

The CA3045 and CA3046 each consist of five general purpose silicon NPN transistors on a common monolithic substrate. Two of the transistors are internally connected to form a differentially connected pair.

The transistors of the CA3045 and CA3046 are well suited to a wide variety of applications in low power systems in the DC through VHF range. They may be used as discrete transistors in conventional circuits. However, In addition, they provide the very significant inherent integrated circuit advantages of close electrical and thermal matching.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer (OCM).

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

CA3045, CA3046

Complete data sheet available via web, Harris home page. http://www.semi.harris.com/ or via Harris AnswerEAX, see Section 10

General Purpose NPN **Transistor Arrays**

#### Features

November 1996

- Low Noise Figure ...... 3.2dB (Typ) at 1kHz

- 5 General Purpose Monolithic Transistors

- Operation From DC to 120MHz

Two Matched Transistors

- Wide Operating Current Range

- Full Military Temperature Range

#### **Applications**

- . Three Isolated Translators and One Differentially Connected Translator Pair for Low Power Applications at Frequencies from DC Through the VHF Range

- Custom Designed Differential Amplifiers

- Temperature Compensated Amplifiers

- · See Application Note, AN5296 "Application of the CA3018 Integrated-Circuit Transistor Array" for Suggested Applications

The CA3045 and CA3046 each consist of five general purpose silicon NPN transistors on a common monolithic substrate. Two of the transistors are internally connected to form a differentially connected pair.

The transistors of the CA3045 and CA3046 are well suited to a wide variety of applications in low power systems in the DC through VHF range. They may be used as discrete transistors in conventional circuits. However, in addition, they provide the very significant inherent integrated circuit advantages of close electrical and thermal matching.

### Ordering Information

| PART NUMBER<br>(BRAND) | TEMP.<br>RANGE (°C) | PACKAGE                     | PKG.<br>NO. |

|------------------------|---------------------|-----------------------------|-------------|

| CA3045                 | -55 to 125          | 14 Ld SBDIP                 | D14.3       |

| CA3045F                | -55 to 125          | 14 Ld CERDIP                | F14.3       |

| CA3046                 | -55 to 125          | 14 Ld PDIP                  | E14.3       |

| CA3046M<br>(3046)      | -55 to 125          | 14 Ld SOIC                  | M14.15      |

| CA3046M96<br>(3046)    | -55 to 125          | 14 Ld SOIC Tape<br>and Reel | M14.15      |

#### Pinout

CA3045, (CERDIP, SBDIP) CA3046 (PDIP, SOIC) **TOP VIEW**